## SID1152K circuit layout suggestion

#### 2017/09/25 Romeo

COMPANY CONFIDENTIAL

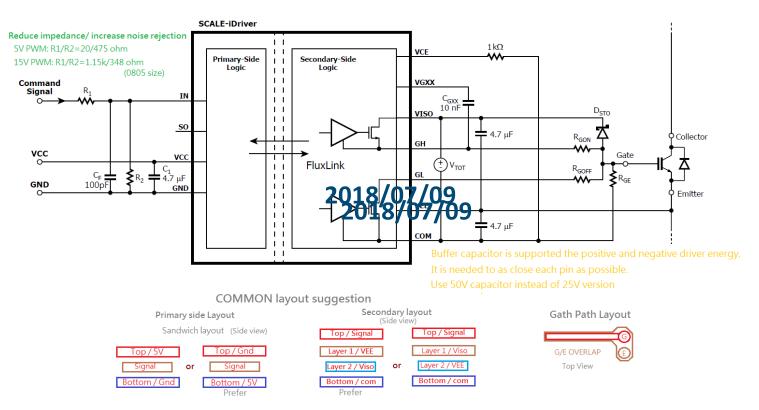

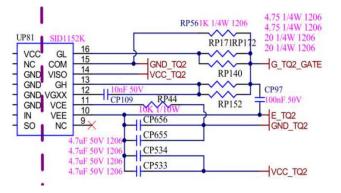

## **IGBT (No Short circuit protection)**

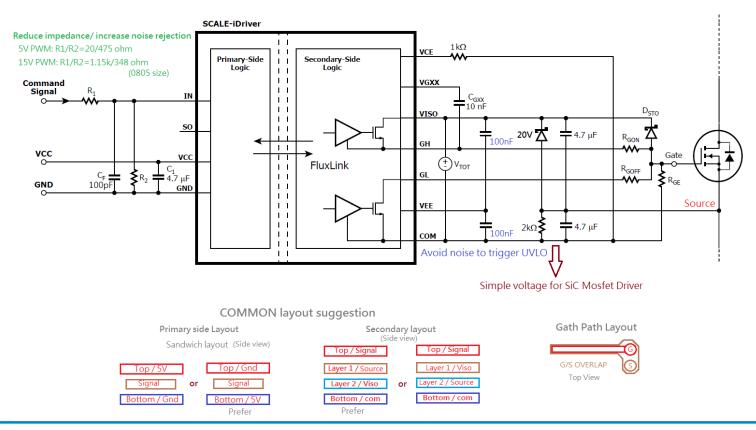

## SiC Mosfet (No Short circuit protection)

#### **Remark:**

- Schottky diode (D<sub>STO</sub>) connected between semiconductor gate and VISO pin. The short-circuit current value can be limited to a safe value.

- Since the desaturation detect function is disable, the diode can be omitted to gain more layout size.

- Disable desaturation function

- $\triangleright$  V<sub>CE</sub> is a input pin.

- Input pins of an IC are often connected to the gate of a MOS transistor or input of a OPAMP. This input often has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, V<sub>CE</sub> pin should be connected one 1k ohm resistor to the power supply or ground line.

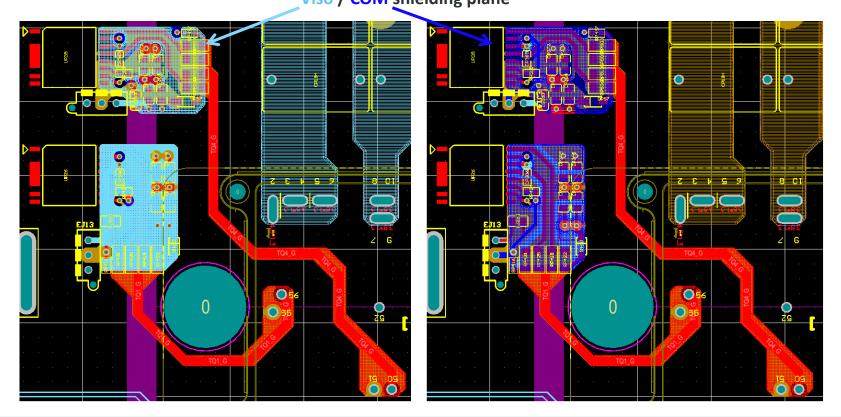

#### **One Channel Layout Explain**

## **Explain Design1**

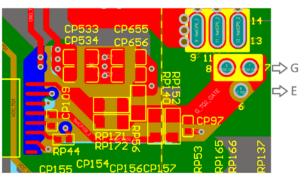

**TOP Layer (Connect all component)**

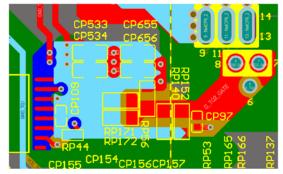

Mid Layer2 (Viso Plane)

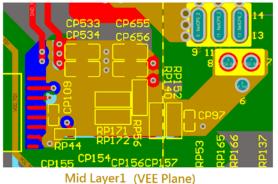

CP154CP156CP1

Bottom Layer (COM Plane)

Remark: Gate and VEE are always together

VEE / Viso / COM Planes are important to improve "EMC behavior"

•

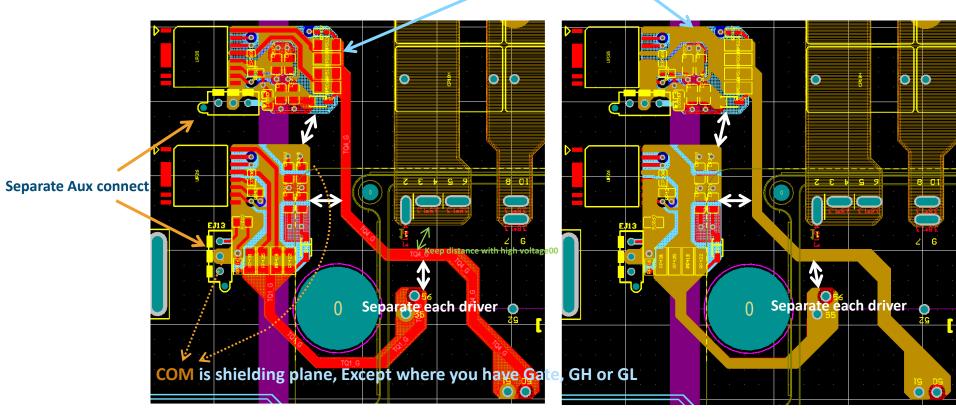

#### Explain2: Top/Mid-Layer1 Gate & VEE always together(VEE only cross gate loop)

# Explain2: Mid-Layer2/Bottom